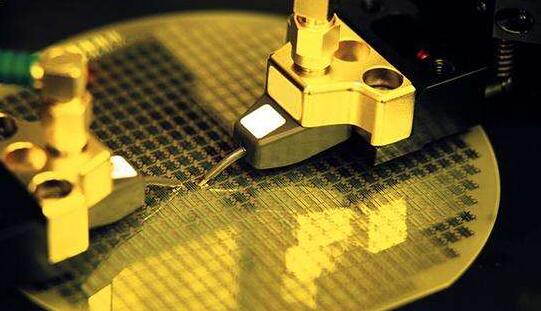

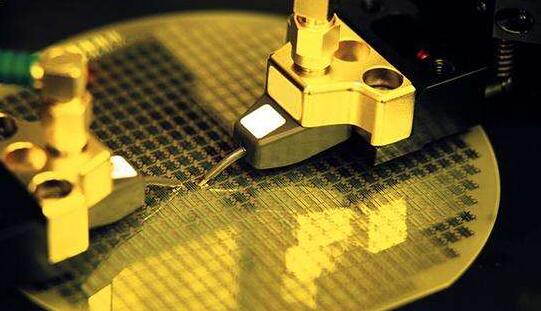

臺(tái)積電下半年5nm接單滿載���,優(yōu)化版4nm明年進(jìn)入量產(chǎn),已獲蘋果��、高通���、聯(lián)發(fā)科��、博通����、英特爾等大廠采用�����,但3nm推進(jìn)面臨芯片設(shè)計(jì)復(fù)雜度及晶圓代工成本大幅拉高等問(wèn)題����,關(guān)鍵在于新款極紫外光(EUV)曝光機(jī)采購(gòu)金額創(chuàng)新高,產(chǎn)出吞吐量(throughput)提升速度放緩�,恐將導(dǎo)致3nm晶圓代工價(jià)格逼近3萬(wàn)美元。

由于3nm晶圓代工價(jià)格過(guò)高恐影響客戶制程微縮速度�����,為了在明年之后加速客戶5nm產(chǎn)品線轉(zhuǎn)換至3nm�,并維持先進(jìn)制程依循摩爾定律推進(jìn)軌道,設(shè)備業(yè)界透露����,臺(tái)積電將啟動(dòng)EUV持續(xù)改善計(jì)劃(Continuous Improvement Plan�,CIP)���,希望在略為增加芯片尺寸的同時(shí)��,減少先進(jìn)制程EUV光罩使用道數(shù)�,以降低3nm「曲高和寡」問(wèn)題�。臺(tái)積電近幾年擴(kuò)大采購(gòu)EUV曝光機(jī),下半年5nm產(chǎn)能全開(kāi)�����,包括蘋果A15應(yīng)用處理器及M1X/M2計(jì)算機(jī)處理器�����、聯(lián)發(fā)科及高通新款5G手機(jī)芯片����、AMD Zen 4架構(gòu)計(jì)算機(jī)及服務(wù)器處理器等將陸續(xù)導(dǎo)入量產(chǎn)。臺(tái)積電為了維持技術(shù)領(lǐng)先����,由5nm優(yōu)化后的4nm將在明年進(jìn)入量產(chǎn),全新3nm也將在明年下半年導(dǎo)入量產(chǎn)�����,然而客戶端對(duì)于延長(zhǎng)使用4nm或采用全新3nm態(tài)度搖擺,關(guān)鍵差別在于EUV光罩層數(shù)多寡決定了晶圓代工價(jià)格高低�����。業(yè)者分析�,EUV曝光機(jī)價(jià)格愈來(lái)愈高��,下半年即將推出的NXE:3600D價(jià)格高達(dá)1.4~1.5億美元�����,產(chǎn)出吞吐量每小時(shí)可達(dá)160片12吋晶圓����,與上代機(jī)型相較增加幅度不大。而由制程上來(lái)看�����,4nm主要是以5nm進(jìn)行優(yōu)化��,EUV光罩層大約在14層以內(nèi)���,但3nm預(yù)計(jì)將采用25層EUV光罩層�����,所以3nm晶圓代工價(jià)格恐怕上看3萬(wàn)美元�����,并不是所有客戶都愿意買單�。為了降低客戶產(chǎn)品線由5nm向3nm推進(jìn)速度放緩的疑慮,臺(tái)積電啟動(dòng)EUV CIP計(jì)劃改善制程���,希望透過(guò)減少EUV光罩層使用道數(shù)及相關(guān)材料�,例如將3nm的25層EUV光罩層減少至20層�。設(shè)備業(yè)者指出,雖然芯片尺寸將因此略為增加��,但若計(jì)劃成功可以有效降低生產(chǎn)成本及晶圓價(jià)格����,加快客戶產(chǎn)品線轉(zhuǎn)向3nm。

臺(tái)積電今后三年的1,000億美元資本支出��,有80%將用于擴(kuò)充先進(jìn)制程產(chǎn)能�,而隨著臺(tái)積電先進(jìn)制程向3nm及2nm發(fā)展�����,又以極紫外光(EUV)產(chǎn)能建置將占千億美元預(yù)算的最大比重�。因此�,若能透過(guò)EUV CIP計(jì)劃,減少EUV采購(gòu)量�����,將有助臺(tái)積提高自由現(xiàn)金流量���。臺(tái)積電要在5nm及更先進(jìn)制程維持領(lǐng)先,近年來(lái)積極買進(jìn)EUV曝光機(jī)并維持產(chǎn)能優(yōu)勢(shì)�。根據(jù)臺(tái)積電于日前召開(kāi)的技術(shù)論壇中指出,EUV曝光機(jī)累計(jì)裝機(jī)數(shù)量到2020年已占全球總機(jī)臺(tái)數(shù)量的50%�,2020年為止采用臺(tái)積電EUV技術(shù)生產(chǎn)的晶圓,占累計(jì)EUV曝光晶圓數(shù)的65%��。隨著臺(tái)積電Fab 18廠第五期至第八期的3nm產(chǎn)能在未來(lái)2~3年逐步完成建置并進(jìn)入量產(chǎn)�,以及美國(guó)亞利桑那州12吋廠第一期在2024年后進(jìn)入量產(chǎn),采用臺(tái)積電EUV技術(shù)曝光的晶圓數(shù)將呈現(xiàn)等比級(jí)數(shù)成長(zhǎng)�����,坐穩(wěn)全球擁有最大EUV產(chǎn)能的半導(dǎo)體廠寶座,但也得付出龐大的投資成本���。然而EUV曝光機(jī)持續(xù)推陳出新�����,不僅耗電量大得驚人�,產(chǎn)出吞吐量(throughput)仍有很大的改善空間���。況且���, 先進(jìn)制程投資金額愈來(lái)愈高,能夠支付如此龐大晶圓代工費(fèi)用的半導(dǎo)體廠已經(jīng)沒(méi)有幾家���,雖然臺(tái)積電現(xiàn)在有蘋果�����、NVIDIA��、AMD���、高通��、聯(lián)發(fā)科�、英特爾�����、博通�、邁威爾(Marvell)、賽靈思(Xilinx)等大客戶采用先進(jìn)制程��,但隨著三星晶圓代工積極擴(kuò)產(chǎn)����,英特爾加駕先進(jìn)制程產(chǎn)能投資��,臺(tái)積電面臨的競(jìng)爭(zhēng)壓力將愈來(lái)愈大��。對(duì)臺(tái)積電而言��,EUV產(chǎn)能建置完成后最怕的就是客戶訂單量能不如預(yù)期�����,產(chǎn)能利用率過(guò)低將造成毛利率下滑壓力���。因此�����,此次啟動(dòng)EUV CIP計(jì)劃����,若能有效減少3nm晶圓EUV光罩層數(shù),在達(dá)成同樣產(chǎn)出量情況下將有助于減少EUV曝光機(jī)采購(gòu)量�,若每年減少1~2臺(tái)EUV機(jī)臺(tái)采購(gòu),資本支出也可降低3億美元���,對(duì)于提高臺(tái)積電自由現(xiàn)金流量��、降低折舊攤提費(fèi)用增加幅度等都將有明顯幫助����。